CoWoS--CoPoS--CoWoP

CoWoS--CoPoS--CoWoP

- 2025-08-01

- 癌大:CoWoP 目前是用 40um 的線寬在測試,達成最終目標應該是要一陣子

比較

-

-

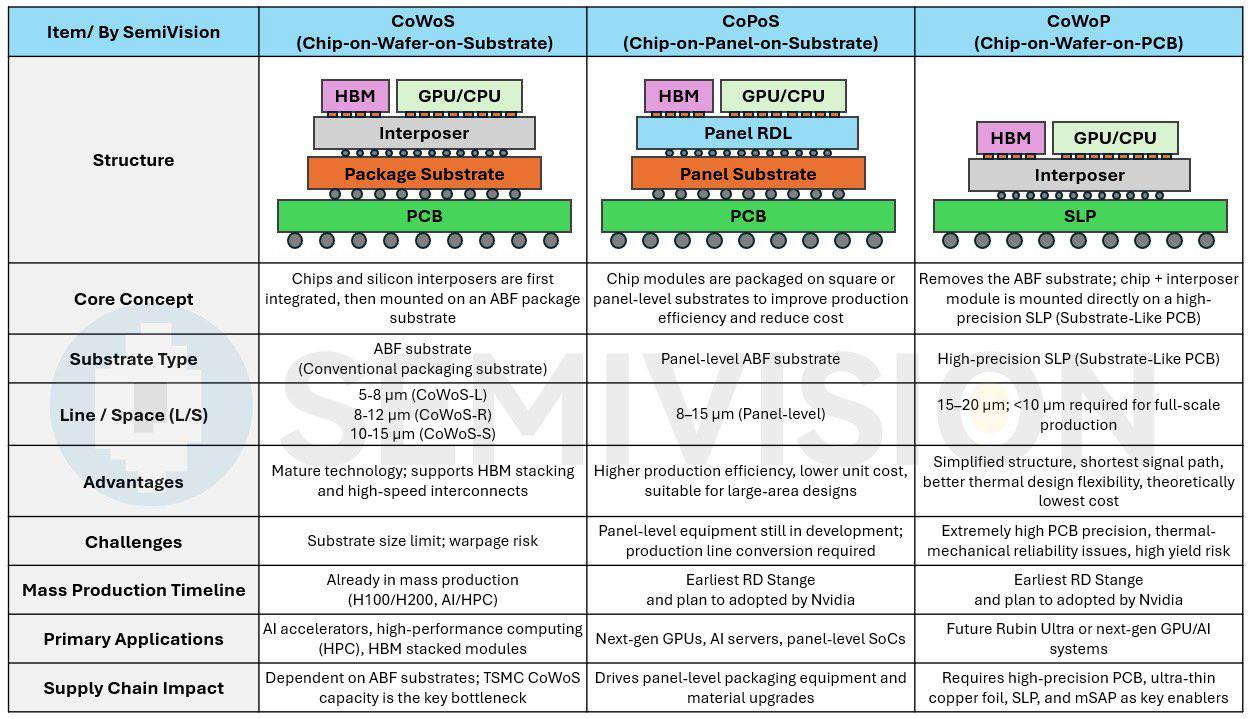

CoWoS (Chip-on-Wafer-on-Substrate)

-

CoPoS (Chip-on-Panel-on-Substrate)

-

CoWoP (Chip-on-Wafer-on-PCB)

| 項目 | CoWoS | CoPoS | CoWoP |

|---|---|---|---|

| 結構 | HBM、GPU/CPU → Interposer → Package Substrate → PCB | HBM、GPU/CPU → Panel RDL → Panel Substrate → PCB | HBM、GPU/CPU → Interposer → SLP |

| 核心概念 | 晶片與矽中介層先整合,再貼裝於 ABF 封裝基板 | 將晶片模組封裝於方形或 Panel 級基板上,以提升生產效率並降低成本 | 取消 ABF 基板;晶片+中介層模組直接貼裝於高精度 SLP (Substrate-Like PCB) |

| 基板類型 | ABF 基板 (傳統封裝基板) | Panel 級 ABF 基板 | 高精度 SLP (Substrate-Like PCB) |

| 線寬/間距 (L/S) | 5–8 µm (CoWoS-L) / 8–12 µm (CoWoS-R) / 10–15 µm (CoWoS-S) | 8–15 µm (Panel-level) | 15–20 µm;全面量產需 < 10 µm |

| 優勢 | 技術成熟;支援 HBM 堆疊與高速互連 | 產能效率高、單位成本低,適合大面積設計 | 結構最精簡、訊號路徑最短、散熱設計彈性佳,理論成本最低 |

| 挑戰 | 基板尺寸受限;翹曲風險 | Panel 級設備仍在開發中;量產線需改造 | PCB 精度要求極高;熱機可靠度議題;良率風險大 |

| 量產時程 | 已量產 (H100/H200,AI/HPC) | 最早研發階段,Nvidia 計畫導入 | 更早期研發階段,Nvidia 計畫導入 |

| 主要應用 | AI 加速器、高效能運算 (HPC)、HBM 堆疊模組 | 次世代 GPU、AI 伺服器、Panel-level SoC | 未來 Rubin Ultra 或次世代 GPU/AI 系統 |

| 供應鏈影響 | 依賴 ABF 基板;TSMC CoWoS 產能為主要瓶頸 | 推動 Panel-level 封裝設備與材料升級 | 需高精度 PCB、超薄銅箔、SLP 與 mSAP 為關鍵使能條件 |