2025-11-09_先進晶片堆疊封裝技術概覽

先進晶片堆疊封裝技術概覽

☘️ Article

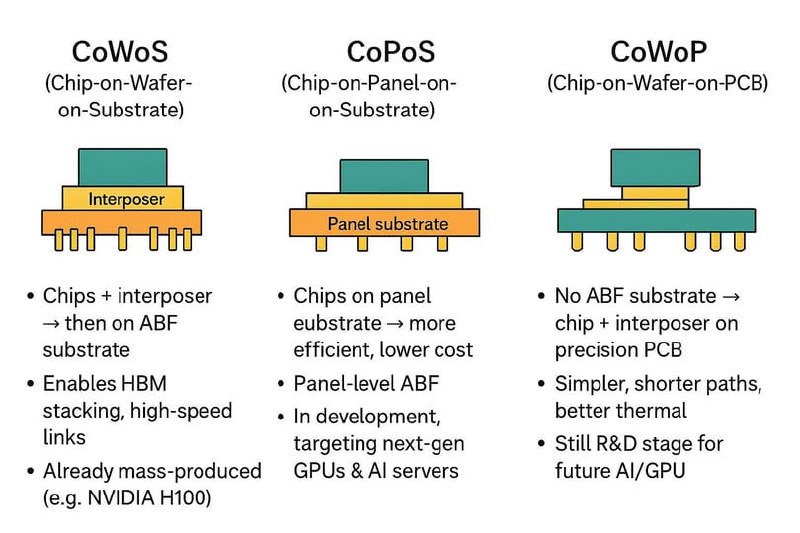

CoWoP, CoPoS 在晶片尺寸變大,切出來顆數越來越少的前提下,發展的可見度高 (圖 Source semiwiki)

- 至於下面提到的 PTFE 材料則是去年一度有傳 Midplane 要用,但後來不了了之,這要看 chip vendor 們的心情。

- 近期再次被拿出來討論,這局聽床師們才有機會贏。

CoWoP (晶圓級晶片封裝基板,Chip on Wafer on PCB)

- 一家供應商展示了採用 M8 級覆銅板 (CCL) 的先進類載板 (SLP),面積大致與伺服器 CPU/GPU 相當,我們認為這是 CoWoP 封裝中的平台印刷電路板 (PCB)。

- 該供應商已收到客戶關於此類特殊 PCB 的開發需求,但無法透露產品的量產時間表。

- 大部分受訪供應商表示,類載板 (SLP) 的線寬/ 線距 (L/S) 極限為 20/20 微米,而 iPhone 主機板類載板的線寬/ 線距約為 35/35 微米,封裝基板的線寬/ 線距可達到 10/10 微米及以下。

- 理論上,封裝基板供應商更有能力生產這些 CoWoP 類載板,但將現有封裝基板生產線「降級」生產類載板可能不具經濟性—— 尤其是已剝離 PCB 業務的供應商 (如揖斐電 (Ibiden,4062.T;由佐藤祥司覆蓋))。

- 我們仍維持以下觀點:① 若主流積體電路 (IC) 廠商採用 CoWoP 技術,具備改良半加成法 (mSAP) 製造能力的 PCB 供應商將受益,包括臻鼎科技、欣興電子、華通電腦 (2313.TW;未覆蓋)、奧特斯 (AT&S,ATSV.VIVI;瑞昱半導體 (Rubin Ultra) 不會採用 CoWoP 技術。

T 玻璃 (低熱膨脹係數玻璃布) 短缺問題

- T 玻璃短缺高峰可能出現在 2026 年中左右,2027 年起將出現更為顯著的緩解。

- 封裝基板供應商正尋求多元化供應來源以應對短缺,且已取得進展—— 例如向日東紡 (Nitto Boseki,3110.T;由長谷川佳仁覆蓋) 採購。

- 一家封裝基板供應商表示,已獲得中國低膨脹係數玻璃供應商格雷斯織物 (Grace Fabric,603256.SS;未覆蓋) 的全力支持,目前樣品測試與認證工作正全速推進,預計 2025 年四季度收到樣品,2026 年一季度可能獲得採用該公司低膨脹係數的覆銅板。

- 值得注意的是,該供應商稱其 40%-50% 的 BT 樹脂產品採用 T 玻璃。

- 有封裝基板供應商提及,部分客戶考慮到成本與材料短缺問題,正尋求用類載板 (SLP) 取代部分 BT 樹脂基板,但這可能只是無奈之舉。

- 欣興電子在 2025 年第二季財報電話會議中表示,正在對中國台灣及大陸地區的低膨脹係數玻璃替代來源進行認證,但認證流程耗時超出預期。

聚四氟乙烯 (PTFE) 材料

- 聚四氟乙烯 (又稱特氟龍) 覆銅板,是指樹脂體系採用聚四氟乙烯材料的覆銅板 (CCL)。

- M10 以上規格的覆銅板,為滿足高速、高頻訊號傳輸所需的極低介電常數 (Dk) 和介電損耗 (Df) 性能,可能必須採用聚四氟乙烯材料。

- 此外,聚四氟乙烯覆銅板的熱穩定性更優,可在更高溫度範圍內保持性能穩定。

- 但由於聚四氟乙烯覆銅板的附著力和尺寸穩定性較差,加工難度顯著高於普通覆銅板,對供應商的鑽孔和層壓製程帶來挑戰,可能導致成本上升及量產困難。

- 因此,受訪 PCB 供應商認為,短期內客戶不會在伺服器系統中採用聚四氟乙烯材料。

- 台光電子 (EMC,2383.TW;未覆蓋) 的 M10 級覆銅板目前仍處於研發階段,尚未納入其展會上展示的產品路線圖。

- 與去年一致,該公司展位上最先進的產品仍是 EM-896K3 (M9 級),其將採用石英玻璃布和 HVLP4 + 銅箔;台光電子同樣認為,M10 級覆銅板必須採用聚四氟乙烯材料。

泰國產能佈局

- 平均來看,PCB / 覆銅板廠商預計其泰國工廠的成本將比中國工廠高出約 20% (高個位數至低雙位數區間)。

- 主要 PCB / 覆銅板供應商的泰國工廠,核心目標應用領域為衛星、伺服器、交換器及光模組用高密度互聯板 (HLC/HDI);此外,華通電腦也在泰國建設柔性印刷電路板 (FPCB) 產能,預計 2026 年四季度完工。

- https://mp.weixin.qq.com/s/Q1u0ezhsKJvwN2VvUB0Y9g

- https://semiwiki.com/wikis/industry-wikis/cowop-chip-on-wafer-on-pcb-wiki/

✍️ Abstract

先進晶片堆疊封裝技術概覽

- CoWoS (Chip-on-Wafer-on-Substrate)

- 此技術將晶片與中介層堆疊在 ABF 基板上,是一種實現高密度整合的先進封裝方法。

- 主要應用於支援高頻寬記憶體 (HBM) 的堆疊,以及提供晶片之間的高速連結。

- 目前已進入大規模量產階段,例如被 NVIDIA H100 等高效能運算產品所採用。

- CoPoS (Chip-on-Panel-on-Substrate)

- 此技術將晶片直接整合在面板級基板上,並採用面板級的 ABF 工藝,旨在提升效率並降低成本。

- 目前仍處於開發階段,主要目標是應用於下一代圖形處理器 (GPU) 和人工智慧 (AI) 伺服器。

- CoWoP (Chip-on-Wafer-on-PCB)

- 這種技術不使用 ABF 基板,而是將晶片與中介層直接堆疊在精密印刷電路板 (PCB) 上。

- 其設計優點包括結構更簡潔、訊號路徑更短,並能提供更好的散熱性能。

- 目前仍在研究與開發階段,目標是為未來的 AI 和 GPU 應用提供創新的解決方案。