EMIB

嵌入式多晶片互聯橋接技術 (Embedded Multi-die Interconnect Bridge)

定義

- 核心概念:Intel 研發的 2.5D 先進封裝技術,專為解決 高效能運算、AI 晶片 間超高速通訊需求設計。

- 技術特徵:捨棄大面積的昂貴矽中介層,改將微型矽橋直接嵌入載板內部,用以連接相鄰的高頻寬需求晶片。

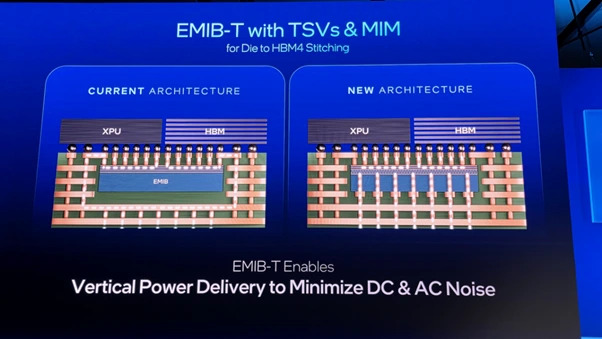

- EMIB-T:EMIB 家族的垂直供電強化版本,在矽橋內加入 TSV 技術,讓電源能以更短、更直接的路徑供應給 HBM 與邏輯晶片,重點在改善高功耗 AI 封裝中的供電穩定性與雜訊問題。

運作原理與製程

- 晶片配置:將微型矽橋置於 2 顆需 極高頻寬、超低延遲傳輸晶片 交界邊緣。

- 製程工法:利用蝕刻技術在載板內部挖出空間,放入矽橋後以具特定熱膨脹係數的封裝膠體固定。

- 連結方式:上方覆蓋絕緣層,透過 打孔、電鍍技術 將矽橋金屬接點向上引出完成訊號連接。

- 技術對標:概念似 台積電 CoWoS-L,皆屬局部區域使用矽橋連接技術。

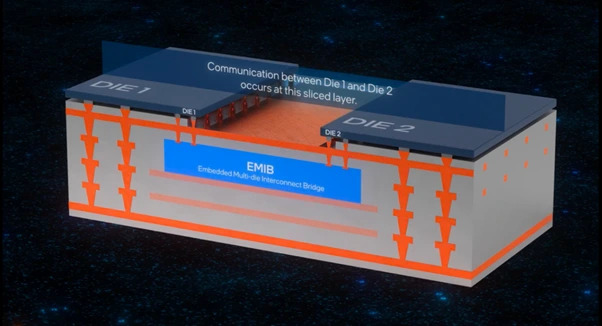

- 切面圖解:

- Die 1、Die 2 間透過嵌入 Substrate 內 EMIB 進行通訊切面結構。

優勢

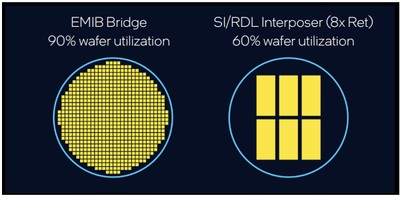

- 晶圓利用率:突破傳統 2.5D 封裝光罩尺寸限制,矽橋晶圓利用率可高達 90% 以上。

- 成本效益:相比同等級的傳統 2.5D 矽中介層解決方案,整體封裝成本可顯著降低 30-40%。

- 擴展藍圖:支援光罩尺寸從 2024 年的 6 倍,一路朝 2026 年的 8 倍、甚至 2028 年挑戰 12 倍的目標邁進。

- 布局差異:

產品線演進

- 基礎架構:EMIB 2.5D 專注於 邏輯與邏輯/邏輯與 HBM 記憶體 之間的高效能平面互連。

- 電供優化:EMIB-M 在矽橋內部整合 MIM 陣列電容,就近提供電荷緩衝以解決 AI 運算的電壓波動問題。

- 垂直供電:EMIB-T 在矽橋內加入 TSV 技術,以最短路徑將穩定電源輸送給 HBM 與邏輯晶片。

- 供電架構:

- EMIB-T 如何透過垂直供電極小化 DC 與 AC 雜訊。

- 異質整合:EMIB 3.5D 結合水平互連的 EMIB 與垂直堆疊的 Foveros 3D 技術,專注於多部運算密度極高晶片的串接。

- 立體視角:

- 展示 3D 堆疊下的層次關係,並特寫 MIM 與 TSV 結構。

玻璃基板技術融合

- 創新架構:Intel 展示厚核心玻璃基板結合 EMIB 設計,鎖定 AI 伺服器與資料中心市場。

- 堆疊規格:採用 10-2-10 架構,包含頂部 10 層重分佈層、中間 2 層高剛性玻璃核心,以及底部 10 層增層。

- 物理優勢:玻璃材料不僅能解決熱膨脹係數不匹配導致的翹曲問題,更能實現極細微凸塊間距。

- 突破性良率:最新測試顯示已成功克服玻璃基板在製造或切割時容易產生的微裂痕技術瓶頸。